断供EDA!传:美国将对华断供GAA技术相关EDA工具! 外界:针对特定客户?

时间:22-08-12 来源:芯榜+

断供EDA!传:美国将对华断供GAA技术相关EDA工具!

外界:针对特定客户?

8月3日消息,据外媒Protocol报道:

拜登政府计划阻止中国获得先进的芯片设计软件,针对特定类型EDA软件实施新的出口限制。

这条新闻被外界解读为,针对中国AI芯片特定企业,致命一击。

美国:正考虑断供GAA相关EDA工具

几个月来,拜登政府一直在权衡一项可能的禁令

Protocol获悉,美国准备对一种用于设计半导体的特定类型软件实施新的出口限制,该软件利用了对生产最先进的人工智能芯片至关重要的下一代技术,旨在瞄准中国芯片制造商。

据一位熟悉拜登政府计划的人士透露,拜登政府数月来一直在考虑一项可能的禁令,但已命令商务部颁布一项新规则,有效阻止芯片设计软件的出口。芯片设计软件是用一种称为gate all around的新兴技术制造芯片所必需的。

新的出口限制规定将在未来几周内实施,目前正在由管理和预算办公室进行审查,不过实施的细节仍在敲定。这位知情人士说,政府的目标是阻止向追求人工智能应用的中国公司出售这些设计工具。

白宫和商务部没有回复相关置评。

GAA:3nm以下高阶制程的选择

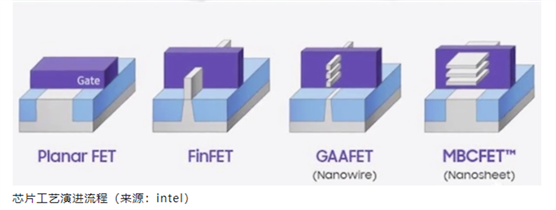

随着GAA FET(全环绕栅极晶体管)逐渐取代3nm及以下的finFET(鳍式场效应晶体管),芯片行业已经准备好迎接晶体管结构的另一次变革,这给设计团队带来了一系列需要充分理解和解决的新挑战。

GAA FET是从finFET演进而来的,但是其对于设计流和工具的影响依然意义重大。

新的栅级结构极大地减少了漏电流。

在7nm和5nm工艺中,由于底部(连接到硅体的部分)没有得到完全控制,finFET泄露开始增加。这是2011年推出finFET的一个原因。对于平面晶体管,即使器件关闭,电流仍然会在源极和漏极之间流动。最终,设计人员被迫使用诸如电源门控和其他技术之类的方法来最大程度地减少电源浪费。

如今,finFET正在失去动力。管在5nm工艺中,finFET的缩小能力已经到达了极限,但仍能提供有意义的缩放优势。2D晶体管到3D晶体,GAA技术发挥重要作用

因此,行业关注的焦点在于将栅级引入通道的第四侧,生成一个全环绕栅极结构。通过提高晶体管通道并创建一个鳍片,将栅极从三个侧面包裹在通道周围,从而增加了栅级和通道之间的接触面积。

三星曾对外宣称:我们是第一家生产GAA产品的公司。现在,我们又是第一个研究MBCFET的。这与Intel研究路径是相关联的,但一切都需要时间证明。

三星3nm开始生产,传首家客户来自中国

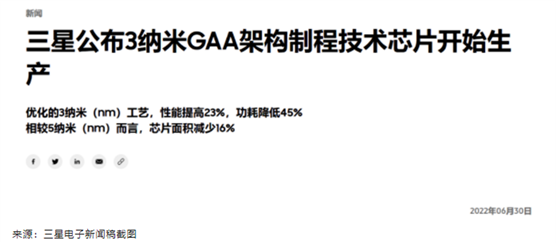

6月30日,三星半导体发布新闻稿正式公布,三星基于3纳米(nm)全环绕栅极(Gate-All-AroundT,简称 GAA)工艺节点的芯片已经开始初步生产。

6月28日,韩国媒体TheElec援引消息人士的话报道称,三星3纳米工艺的首个客户是中国比特币挖矿用半导体厂商——上海磐矽半导体有限公司(PanSemi)。

目前,上海磐矽半导体有限公司官网仅有一个展示页面,称该公司总部位于上海,是一家芯片设计能力为28纳米、16纳米和10纳米的高科技初创公司,专注于数字加密货币和Al应用的专用芯片设计。

企查查显示,该公司核心团队只有陈建兵1人,参保人数也仅有3人。

三星方面对此并没有披露任何信息。

早前台积电的5纳米客户也是由中国的比特大陆首发。吴忌寒曾经在比特大陆主办的法兰克福矿业大会上透露,2020年一季度5纳米将开始量产,3纳米芯片的研发也正在路上,即便是2纳米和1纳米的芯片也已排上日程。

比特大陆2019年下半年给台积电下的订单大概在5万片,包括16纳米和7纳米芯片,可以出产约60万台矿机。

对比5纳米芯片,3纳米面积减少16%,功耗降低45%

三星计划通过抢先发布3纳米工艺来进一步抢占晶圆代工市场。中国客户成三星3nm试验田,是因为有钱??

到这里,你知道为啥美国正制定相关制裁EDA政策了把。

什么是EDA工具?中国EDA什么水平?

一位从事CPU设计的工程师表示,“在没有EDA工具之前,搞电路要靠人手工,对于大规模集成电路有上亿晶体管的设计用手工简直是不可为的......可以说有了EDA工具,才有了超大规模集成电路设计的可能”。

EDA工具是电子设计自动化(Electronic Design Automation)的简称。利用EDA工具,工程师将芯片的电路设计、性能分析、设计出IC版图的整个过程交由计算机自动处理完成。

由于上世纪六十七年代,集成电路的复杂程度相对偏低,这使得工程师可以依靠手工完成集成电路的设计、布线等工作。但随着集成电路越来越复杂,完全依赖手工越来越不切实际。

1986年,硬件描述语言Verilog问世,Verilog语言是现在最流行的高级抽象设计语言。1987年,VHDL在美国国防部的资助下问世。这些硬件描述语言的问世助推了集成电路设计水平的提升。随后,根据这些语言规范产生的各种仿真系统迅速被推出,使得设计人员可对设计的芯片进行直接仿真。

时至今日,尽管所用的语言和工具仍然不断在发展,但是通过编程语言来设计、验证电路预期行为,利用工具软件综合得到低抽象级物理设计的这种途径,仍然是数字集成电路设计的基础。

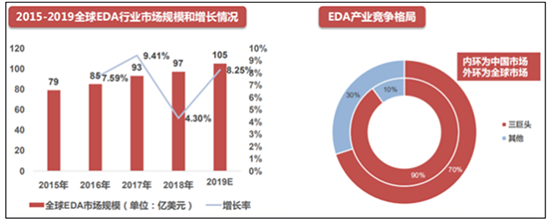

21世纪以来,全球EDA市场兴起了好几波产业整合的风潮。其中,EDA三巨头——Synopsys(新思科技)、Cadence(楷登电子)和西门子旗下的Mentor Graphics(已于2021年更名为Siemens EDA),共发起了超上百次的兼并收购案。经过多次的收购整合,三巨头的在市场上的影响力日益集中。

中国EDA什么水平?

谈到国内的EDA行业,首先要说的是华大九天,即我们业界非常熟悉的命名为“国宝级”的熊猫IC CAD系统。

华大九天成立于2009年,其前身是原华大电子“熊猫”EDA设计平台。作为国家队,华大九天目前已发展成为我国规模最大、技术最强的EDA龙头企业。可以提供全流程数模混合信号芯片设计系统、SoC后端设计分析及优化解决方案、平板(FPD)全流程设计系统、IP以及面向晶圆制造企业的相关服务,其客户覆盖国内众多集成电路企业。

另一家有特色的EDA公司是山东济南概伦电子科技有限公司。概伦于2010年3月成立,产品包括电路仿真/良率导向设计技术和半导体器件模型/噪声测试解决方案,下一步产品方向为新一代大规模高精度仿真及设计验证平台、针对纳米级制造技术的半导体器件建模库平台及测试验证系统等。

概伦公司的发起人刘志宏,曾在美国硅谷与胡正明团队合作,开发了BSIM3仿真模型,后来的BSIMPro SPICE就是以此为基础发展得来。刘志宏博士曾担任Cadence全球副总裁。

下为国内部分EDA企业技术介绍,供参考

从市场价值来看,整个EDA软件的全球市场规模不足一百亿美元,却撬动了5000亿美元的半导体产业。如果没有了这颗基石,全球所有的芯片设计公司都会直接停摆,半导体金字塔就会坍塌。

EDA行业已经从上世纪的百家争鸣缩减到目前三大巨头,成为一个高度垄断的行业。

摘自-芯榜+

| 上一篇 | 下一篇 |

|---|---|

| 三次倒在交易所门口,行业龙头连1亿美元 都募... | 每日优鲜如何一步步走到现在? |